## No. AN6565.1 March 1997

# **Application Note**

## Design of Clock Generators for Use with COSMAC Microprocessor CDP1802

Author: D. Hillman

### Introduction

Clock signal generation for the CDP1802 COSMAC Microprocessor is simple and straightforward. The CDP1802 features of static operation, single-phase clock input, and the on-chip oscillator amplifier make practical the use of a lowcost, highly stable, crystal-controlled oscillator as its clock generator. The design of external oscillators for this purpose, crystal or RC controlled, is equally straightforward and they require only minimal circuitry. In addition to the oscillator amplifier, the CDP1802 incorporates all necessary start/stop logic on-chip. This application note describes clock generator designs suitable for various applications.

#### **Crystal Oscillator Design**

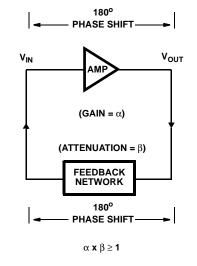

The basic oscillator circuit for the CDP1802 consists of the on-chip amplifier and an external feedback network as illustrated in Figure 1. For oscillation to occur, the gain of the amplifier ( $\alpha$ ) times the attenuation ( $\beta$ ) of the feedback network must be greater than or equal to one. In addition, the total phase shift through the amplifier and feedback network must be equal to N times 360 degrees, where N is an integer. Oscillations occur in any system in which the amplified signal is returned in phase to the amplifier after being attuned less than it was originally amplified.

The frequency stability of an oscillator is primarily dependent upon the phase-changing properties of the feedback network. Because of their high Q and inherent frequency stability, quartz crystals are commonly used in the feedback network.

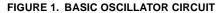

A parallel resonant oscillator circuit is shown in Figure 2. The phase angle for the type of feedback network shown in this figure is extremely sensitive to a change in frequency, a condition necessary for stable oscillation. If the equivalent resistance of the crystal is in fact zero (infinite Q), a change in phase angle of the feedback circuit would not cause any change in oscillator frequency. Therefore, for an oscillator of highest stability, the Q of the crystal should be as high as possible. In general, Q increases with increasing frequency.

#### FIGURE 2. PARALLEL RESONANT OSCILLATOR CIRCUIT

The crystal load capacitance,  $C_L$ , is defined as the series sum of  $C_1$  and  $C_2$ . Higher values of crystal load capacitance generally improve frequency stability, but also increase power consumption. The choice of equivalent load capacitance (usually specified to the crystal suppliers) only fixes

1-888-INTERSIL or 321-724-7143 | Intersil (and design) is a trademark of Intersil Americas Inc. Copyright © Intersil Americas Inc. 2001. All Rights Reserved the series sum of the two capacitors  $C_1$  and  $C_2$ . The value of the amplifier output capacitance  $C_1$  should not be fixed. A trimmer should be connected in parallel with, or used in place of, a fixed output capacitor to permit compensation for variation in stray capacitance and circuit component values.

The required capacitance range for the oscillator trimmer capacitor is determined by the variation in oscillation frequency with load capacitance. The total trimming range is mainly a function of the crystal characteristics. For a more detailed analysis, see Reference 4.

#### **Practical Oscillator Circuits**

The amplifier, feedback network, and crystal considerations discussed in the preceding paragraphs can be combined for the design of a crystal-controlled oscillator for the CDP1802. The majority of microprocessor applications do not require the frequency of oscillation to be so exact as to require oscillator trimming. An "untrimmed" crystal oscillator will be within 1% of its specified crystal frequency. For most microprocessor applications the following simple guidelines can be used.

- 1. The crystal should be connected between terminals 1 and 39 of the CDP1802.

- 2. For crystal frequencies between 100KHz and 6.4MHz, a  $10M\Omega$  to  $22M\Omega$  feedback resistor should be used in parallel with the crystal.

- Capacitors C<sub>1</sub> and C<sub>2</sub> are not required but a value of between 20pF and 30pF for each is recommended to improve stability.

It should be noted that the on-chip oscillator and timing generator are capable of operating at frequencies higher than the microprocessor maximum operating frequency. For reliable operation, the crystal frequency must always be less than or equal to the maximum operating frequency specified in the CDP1802 data sheet.

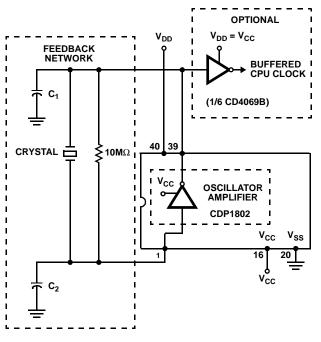

A practical example, the CDP18S020 Evaluation Kit oscillator, consists of a 10M $\Omega$  feedback resistor and a 2MHz AT cut crystal, both connected in parallel across terminals 1 and 39 of the CDP1802. (Crystal: Part No. X023303; C<sub>L</sub>=15pF; Series M1; holder, series HC330; made by Turotel, Inc., 13402 S. 71 Highway, Grandview, Missouri 68030.) Provisions for oscillator capacitors are made in the Evaluation Kit, but their use is not required. The increase in oscillator stability with respect to supply voltage that can be obtained by adding the capacitors is shown in Figure 3.

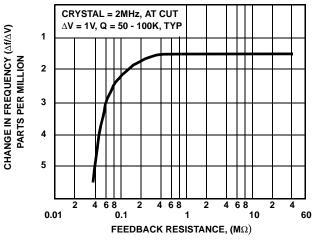

FIGURE 3. STABILITY OF CDP1802 CRYSTAL OSCILLATOR AS A FUNCTION OF LOAD CAPACITANCE VALUE

The amplifier stability also depends upon the value of the resistor in the feedback network. Figure 4 shows the relationship between the feedback resistor value and oscillator stability. The curve indicates that  $10M\Omega$  is an adequate value for the feedback resistor.

FIGURE 4. STABILITY OF CDP1802 CRYSTAL OSCILLATOR AS A FUNCTION OF FEEDBACK RESISTANCE VALUE

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

#### **External Clock Generators**

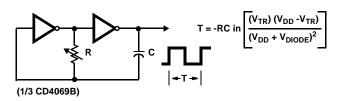

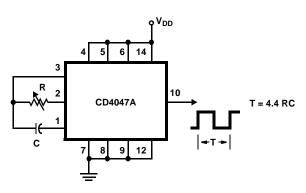

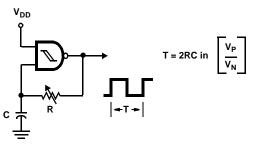

For low-frequency applications (less than 500kHz) a costeffective approach may be to use external RC-controlled oscillators. Three simple RC-controlled oscillators that may be used to clock the CDP1802 are shown in Figure 5. When an external clock is used in high-noise environments, a 20pF to 30pF capacitor between terminal 39 (XTAL) of the CDP1802 and ground may be used to increase the microprocessor noise immunity.

FIGURE 5A. INVERTER TYPE OSCILLATOR (SEE REFER-ENCES 5 AND 6)

FIGURE 5B. RC OSCILLATOR USING DIGITAL IC CD4047A (SEE REFERENCES 5 AND 6)

(1/4 CD4093B)

- FIGURE 5C. SCHMITT-TRIGGER-TYPE RC OSCILLATOR (SEE CD4093B DATA SHEET)

- FIGURE 5. THREE SIMPLE RC-CONTROLLED OSCILLATOR CIRCUITS SUITABLE FOR USE AS EXTERNAL CLOCK FOR CDP1802 MICROPROCESSOR (OUT-PUT CONNECTED TO PIN 1 THROUGH EVALUATION KIT P2-W)

The selection of the R and C should be compatible with system requirements. The capacitor should be non-polarized and have low leakage. There is no upper limit for either R or C values to maintain oscillation. However, C should be larger than the inherent stray capacitance. R must be larger than the output impedance of the COS/MOS device, which is typically hundreds of ohms. In addition, with very large values of R, some short-term instability with respect to time may be noted. Based on these considerations recommended values for these components are:

- C greater than 100pF, up to any practical value

- R greater than 10k $\Omega$ , but less than 1M $\Omega$

With large values of R and C, the circuit in Figure 5(c) can be used. This circuit, because of its hysteresis, eliminates multiple output pulses caused by noise on the input RC waveform. For a more detailed analysis, see References 5 and 6.

#### **Clock Buffering**

In some applications it may be desirable to supply the CPU clock signal to other system components. In such cases the loading on the oscillator circuit should be minimized by buffering the clock through a COS/MOS inverter, as shown in Figure 2. The loading presented by the inverter will be mainly capacitive, about 5pF, and can usually be neglected in non-critical designs. The buffer should be located close to the crystal in order to minimize stray capacitance.

When the crystal oscillator is being trimmed to its desired frequency, the buffered clock technique should also be used to prevent the oscillator from being loaded by the frequency counter.

### References

For Intersil documents available on the internet, see web site http://www.intersil.com/

Intersil AnswerFAX (321) 724-7800.

- [1] *CDP1802 Data Sheet*, Intersil Corporation, AnswerFAX Doc. No. 1305.

- [2] CD4047A Data Sheet, Intersil Corporation, AnswerFAX Doc. No. 623.

- [3] *CD4093B Data Sheet*, Intersil Corporation, AnswerFAX Doc. No. 836.

- [4] AN6086 Application Note, Intersil Corporation, "Timekeeping Advances Through COS/MOS Technology", AnswerFAX Doc. No. 96086.

- [5] AN6230 Application Note, Intersil Corporation, "Timekeeping Advances Through COS/MOS Technology", AnswerFAX Doc. No. 96230.

- [6] AN6267 Application Note, Intersil Corporation, "Astable and Monostable Oscillators Using Intersil COS/MOS Digital Integrated Circuits", AnswerFAX Doc. No. 96267.

- [7] MPM-201 Intersil Corporation, "User Manual for the Intersil CDP1802 COSMAC Microprocessor".