# PCB Design for Manufacture V1.0

From seeedstudio

FUSION EAST PROTOTYPING

#### One-Stop prototype in Seeed Fusion

# CONTENT

| 1. | Brief Introduction                                                         | 3  |

|----|----------------------------------------------------------------------------|----|

| 2. | Seeed Fusion PCB Specification                                             | 3  |

|    | 2.1 PCB Gerber File                                                        | 3  |

|    | 2.2 PCB Specification for FR4-TG130                                        | 4  |

| 3. | Panelization and Bridge Design                                             | 7  |

|    | 3.1 V-CUT Scoring                                                          | 7  |

|    | 3.2 Stamp Hole Design                                                      | 8  |

|    | 3.3 Panelization                                                           | 9  |

|    | 3.4 Panelization Methods for Irregularly Shaped PCBs                       | 12 |

| 4. | Component Layout Considerations                                            | 12 |

|    | 4.1 General Component Layout Requirements                                  | 12 |

|    | 4.2 Reflow Soldering                                                       | 14 |

|    | 4.2.1 General Requirements for SMD Components                              | 14 |

|    | 4.2.2 SMD Component Placement Requirements                                 | 14 |

|    | 4.3 Wave Soldering                                                         | 17 |

|    | 4.3.1 SMD Component Layout Requirements for PCBs Undergoing Wave Soldering | 17 |

|    | 4.3.2 Common Through-Hole Component Layout Requirements                    | 19 |

|    | 4.3.3 General Requirements For Wave Soldering Through Hole Components      | 20 |

| 5. | Hole Design                                                                | 21 |

|    | 5.1 Vias                                                                   | 21 |

|    | 5.1.1 Hole Spacing                                                         | 21 |

|    | 5.1.2 Via Clearance Area                                                   | 22 |

|    | 5.2 Mechanical Hole Design                                                 | 22 |

|    | 5.2.1 Hole Types                                                           | 22 |

|    | 5.2.2 Spacing Requirements                                                 | 22 |

| 6. | Solder Mask Design                                                         | 23 |

|    | 6.1 Solder Mask Design for Copper Traces                                   | 23 |

|    | 6.2 Solder Mask Design for Holes                                           | 23 |

|    | 6.2.1 Via Holes                                                            | 23 |

|    | 6.2.2 Alignment Holes                                                      | 24 |

|    | 6.2.3 Positioning Holes                                                    | 24 |

|    | 6.2.4 Buried and Plugged Vias                                              | 25 |

|    | 6.3 Solder Pad Solder Mask Design                                          | 25 |

|    | 6.4 Gold-Finger Solder Mask Design                                         | 27 |

| 7. | Copper Trace Design                                                        | 27 |

|    | 7.1 Trace Width, Spacing and Routing Requirements                          | 27 |

|    | 7.2 Solder Pad to Trace Connections                                        | 28 |

|    | 7.3 Copper Pour Design Requirements                                        | 31 |

| 8. | Silkscreen Design                                                          | 31 |

|    | 8.1 Silkscreen Design Considerations                                       |    |

|    | 8.2 Silkscreen Contents                                                    | 31 |

| 9. | PCB Lamination Structure                                                   | 33 |

|    | 9.1 Layer Structure                                                        | 33 |

|    | 9.2 Layer Thickness Requirements                                           | 33 |

|    |                                                                            |    |

# FUSION LAST PROTOTYPING

#### One-Stop prototype in Seeed Fusion

| 10. | PCB Dimensions Specification                         | 34 |

|-----|------------------------------------------------------|----|

|     | 10.1 Manufactured PCB Dimensions                     | 34 |

| 11. | Fiducial Mark Design                                 | 36 |

|     | 11.1 Classification                                  | 36 |

|     | 11.2 Fiducial Mark Structure                         | 36 |

|     | 11.2.1 Panel Fiducial Marks and Image Fiducial Marks | 36 |

|     | 11.2.2 Local Fiducial                                | 36 |

|     | 11.3 Position of Fiducials                           | 37 |

|     | 11.3.1 Panel Fiducial Marks                          | 37 |

|     | 11.3.2 Image Fiducial Marks                          | 38 |

| 12. | Surface Treatment                                    | 38 |

|     | 12.1 Hot Air Solder Leveling (HASL)                  | 38 |

|     | 12.1.1 Process Requirements                          | 38 |

|     | 12.1.2 Range of Applications                         | 38 |

|     | 12.2 Electroless Nickel Immersion Gold (ENIG)        | 39 |

|     | 12.2.1 Process Requirements                          | 39 |

|     | 12.2.2 Range of Applications                         | 39 |

|     | 12.2.3 Organic Solderability Preservatives (OSP)     | 39 |

| 13. | Files for Manufacture Requirements                   | 39 |

|     | 13.1 Naming Requirements for Assembly Files          | 39 |

|     | 13.2 Naming Requirements for Stencil Layout Files    | 39 |

|     | 13.3 Naming and Content Requirements for Drill Files | 39 |

| 14. | Appendix                                             | 40 |

|     | 14.1 PCBA Constructions                              | 40 |

#### 1. Brief Introduction

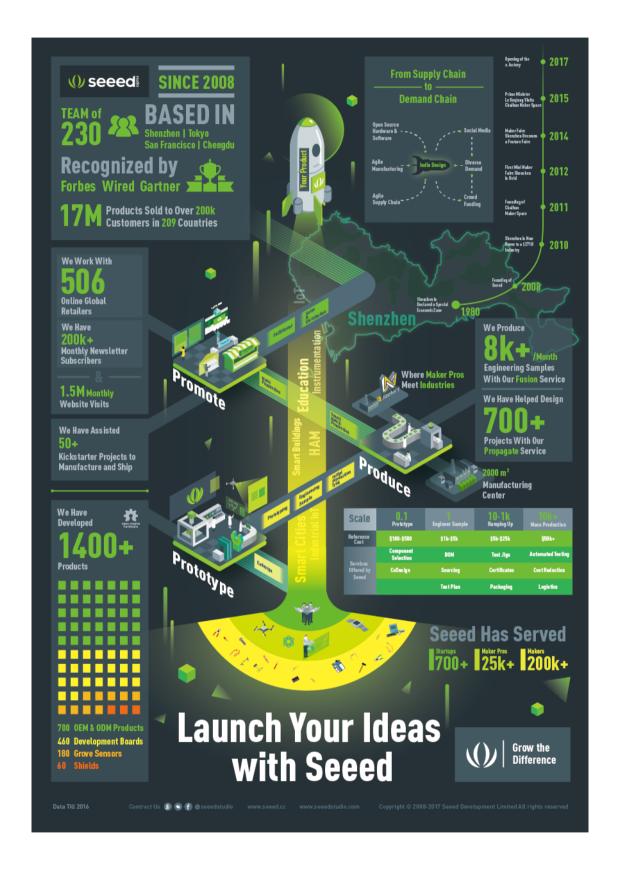

Seeed is a hardware innovation platform for makers to grow inspirations into differentiating products and offers accessible technologies with quality and delivery guarantee. Seeed Fusion Service offers one-stop prototyping service for PCB (Printed Circuit Board) service, PCBA (PCB Assembly) service and other electronic and mechanical customized services (like CNC Milling, 3D Printing, PCB Layout Service).

Seeed has been in the electronics industry for more than 9 years and has accumulated a great deal of manufacturing experience. To help bridge the gap between design and manufacture and put into practice our company values "Grow the Difference", which aims to help more people make their product come true, we have summarized our 9 years of manufacturing experience in this manual.

Since we are not a professional publisher, there may be some incorrect spellings or vague expression in this manual, we really appreciate your feedback to help us improve the manual together. We will keep upgrading this manual to make it beneficial to the whole community, if you have any advice or suggestions, please contact us at: (fusion@seeed.cc). For more information about the latest prototype service and specification, please head to our website www.seeedstudio.com

This specification defines the design parameters for PCB design from a DFM point of view, including the shape, lamination construction, Fiducial design, component layout, conductive traces, holes, solder mask, surface treatments, silk screen design, and so on.

#### **Seeed Fusion PCB Specification**

#### 2.1 **PCB** Gerber File

The Gerber format is an open 2D binary vector image file format. It is the standard file used by printed circuit board (PCB) industry software to describe the printed circuit board images: copper layers, solder mask, legend, etc.Gerber files should be inside a single .rar or.zip archive with standard file extensions:

Notes: 1. Gerber file must be in RS-274x format.

- 2. Drill file (pcbname.TXT) should be in Excellon format.

- 3. Gerber file and Drill file (pcb name.TXT) must be put in the same file.

- 4. Board outline is a must

| Extension   | Layer             |

|-------------|-------------------|

| pcbname.GTL | Top Copper        |

| pcbname.GTS | Top Soldermask    |

| pcbname.GTO | Top Silkscreen    |

| pcbname.GBL | Bottom copper     |

| pcbname.GBS | Bottom Soldermask |

| pcbname.GBO | Bottom Silkscreen |

FUSION EAST PROTOTYPING

| pcbname.TXT     | Drills                        |

|-----------------|-------------------------------|

| pcbname.GML/GKO | Board Outline                 |

| pcbname.GL2     | Inner Layer 2 ( for ≥4 layer) |

| pcbname.GL3     | Inner Layer 3 ( for ≥4 layer) |

# 2.2 PCB Specification for FR4-TG130

| Items                           | Description                              | Specs                                                                                                                           |  |

|---------------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|

|                                 | Description                              | Unit: mm                                                                                                                        |  |

| Board Dimension                 | Min size                                 | 10mm*10mm  Tip: If your board width is smaller than this size, you can make a bigger panel and use slots to separate the board. |  |

|                                 | Max size                                 | 500*500mm                                                                                                                       |  |

| Available Board Layers          | 1-16 layers                              |                                                                                                                                 |  |

| Assailable Describ Oter         | Minf 5pcs                                |                                                                                                                                 |  |

| Available Board Qty             | Max: 8000pcs                             |                                                                                                                                 |  |

| Dielectric Constant             | 4.2-4.7                                  |                                                                                                                                 |  |

| Dielectric Separation thickness |                                          | 0.075 - 5.0                                                                                                                     |  |

|                                 | 1-2 layers                               | 0.6, 0.8, 1, 1.2, 1.6, 2, 2.5, 3                                                                                                |  |

|                                 | 4 layers                                 | 0.8, 1, 1.2, 1.6, 2, 2.5, 3                                                                                                     |  |

|                                 | 6-8 layers                               | 1, 1.2, 1.6, 2, 2.5, 3                                                                                                          |  |

| Available Board Thickness       | 10 layers                                | 1.2, 1.6, 2, 2.5, 3                                                                                                             |  |

|                                 | 12 layers                                | 1.6, 2, 2.5, 3                                                                                                                  |  |

|                                 | 14 layers                                | 2, 2.5, 3                                                                                                                       |  |

|                                 | 16 layers                                | 2.5,3                                                                                                                           |  |

| Available Board Copper Weigh    | 1oz. 2oz. 3oz.                           |                                                                                                                                 |  |

| Board Thickness Tolerance       | ± 10%                                    |                                                                                                                                 |  |

| Minimum trace spacing / width   | Minimum Spacing 4mil  Minimum Width 4mil | For 1oz, 4/4mil, 5/5mil, 6/6mil<br>For 2oz, 10/10mil<br>For 3oz, 15/15mil                                                       |  |

4

| Minimum trace width in inner layers (for 4 layers board) | Minimum Spacing  Minimum Width                                         | ≥6mil                                      |

|----------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------|

| Minimum distance between trace and copper pour           |                                                                        | For 1oz ≥8mil For 2oz ≥12mil For 3oz ≥15mi |

| Minimum distance<br>between vias                         | ≥12mil                                                                 | ≥12mil<br>Aim to prevent Ion migration     |

| Minimum distance between PTH and trace                   | > 12mil                                                                | ≥12mil<br>Aim to prevent Ion migration     |

| Annular Rings                                            |                                                                        | ≥0.152mm/6mil                              |

| Outer Layer Copper Thickness                             | Top Layer: 10Z/0.035mm Layer 2 Layer 3 Bottom Lauer: 10Z/0.035mm       | 0.035-0.07(1oz-2oz)                        |

| Inner Layer Copper Thickness                             | Top Layer Layer 2: 0.5oz/0.017mm  Layer 3: 0.5oz/0.017mm  Bottom Layer | 0.017(0.5oz)                               |

| Drilling Hole Diameter                                   |                                                                        | 0.2 - 6.5mm                                |

| (Mechanical)                                  |                                                             |                                                                                                                            |

|-----------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Width of Solder Mask Dam                      |                                                             | Normal: ≥0.32mm for Green ≥0.35mm for Other colors Limitation (cost extra fee): ≥0.10mm for Green ≥0.13mm for Other colors |

| Diameter of Castellated Holes                 |                                                             | ≥0.60mm                                                                                                                    |

| Size of BGA                                   |                                                             | For 6/6mil ≥0.45mm<br>For 5/5mil ≥0.35mm<br>For 4/4mil ≥0.25mm                                                             |

| Circuit to edge                               | Red line is the outline  Green line is the circuit  >0.4mm. | ≥0.3mm                                                                                                                     |

| Minimum distance between inner trace and NPTH | 0.2mm                                                       | ≥0.2mm/7.87mil                                                                                                             |

| Minimum silkscreen<br>height/trace width      | C 1 Min Height Min trace width                              | height ≥0.5842mm /23mil<br>trace width ≥0.1016mm /4mil                                                                     |

| Perfect aspect ratio of silkscreen            | 1:5                                                         |                                                                                                                            |

| Silkscreen color                              |                                                             | Silkscreen color is WHITE when solder mask is Green, Red, Yellow, Blue, Black                                              |

|                                               |                                                             | Silkscreen color is BLACK when solder mask is white                                                                        |

6

| Minimum distance between pad and silkscreen | 7nil                                         | ≥0.1524mm/6mil |

|---------------------------------------------|----------------------------------------------|----------------|

| Minimum milling slot width                  |                                              | ≥0.8mm         |

| Slot Tolerance(Mechanical)                  |                                              | ±0.15mm        |

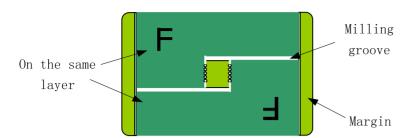

| The minimum board dimension of V-CUT        |                                              | ≥70*55mm       |

| The maximum board dimension of V-CUT        | The V-cut line only is cut from edge to edge | ≤380*380mm     |

| The minimum sub-board dimens ion of V-CUT   | cuge                                         | ≥8*8mm         |

| PCB production time (build time)            | 3-14 working days                            |                |

### 3. Panelization and Bridge Design

#### 3.1 V-CUT Scoring

- [1]V-cut scoring can be used can be used on PCB panels to separate individual boards. They must run across the entire length of the panel, parallel to a flat edge and not interfere with any component placement.

- [2] For panels incorporating v-cut scoring in their design, the recommended board thickness is greater than 3.0mm.

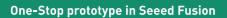

- [3] For PCB panels that require machine automated depaneling, a clearance area of 1.0mm is required along both sides of the v-cut line (and on both top and bottom surfaces) to protect the components from damage.

Figure 1: Clearance area requirements for PCB panels undergoing automated depaneling.

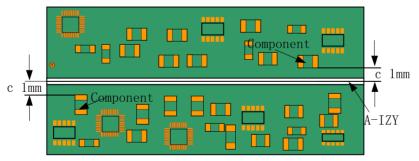

At the same time, the structure of the blade of the v-cut scorer must be considered. As shown in figure 2, no components with a height of over 25mm are allowed within a 5mm distance from the v-cut line.

Figure 2: Demand of blade of automatic board cutter to device in the banned layout area of PCB edge When v-cut design is applied, these conditions must be met in order to protect components during the splitting process, and ensure that the boards will split freely.

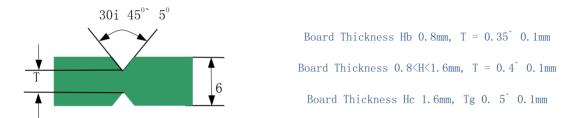

Figure 3: Board thickness requirements for v-cut scoring.

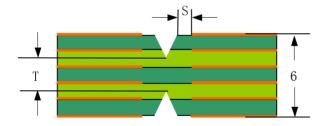

A safe distance of 'S,' as shown in Figure 4, must be maintained between the v-cut line and any copper traces to avoid damaging the trace.  $S \ge 0.3$ mm is usually satisfactory.

Figure 4: The safe distance (S) between v-cut grooves and copper traces.

#### 3.2 Stamp Hole Design

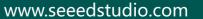

- [4] The recommended width of milling grooves is 2mm. Milling grooves are often used in situations where a certain distance must be maintained between individual boards on a panel. It is generally used together with V-CUT scoring and stamp holes.

- [5] The distance between the origins of adjacent stamp holes should be 1.5mm. Recommended distance between the two groups of stamp hole is 5mm, as shown in picture 5.

Figure 5: Stamp hole design parameters.

#### 3.3 Panelization

There are three recommended modes of panelization: The same direction splice, central symmetric splice, mirror symmetry splice.

- [6] For PCB boards smaller than 80mm x 80mm, panelization is recommended.

- [7] The designer should consider the utilization rate of the design when choosing the PCB material. This is a key factor affecting the cost of the PCB.

Note: For some irregular shapes (such as an 'L' shaped board), applying the appropriate panelization mode can drastically improve the utilization ratio of a panel and reduce costs, as shown in picture 6.

Figure 6: L type PCB layout on a single panel.

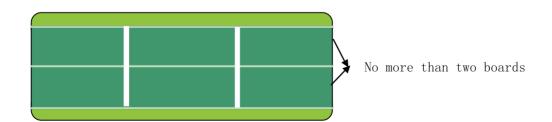

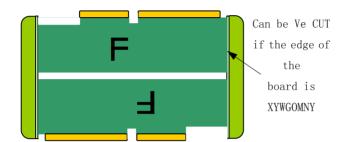

[8] If the PCB is to be processed with reflow soldering and wave soldering techniques, and the cell board size less than 60.0 mm, then no more than two rows should be stacked in one panel (that is, the board should be no more than two boards in height.

Figure 7: Diagram of panelization width.

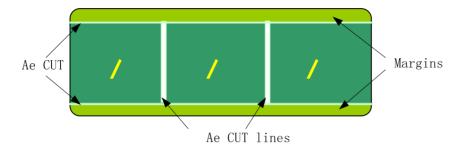

[9] For smaller boards, the number of boards running across the longest side can be greater than 3, but the width

should be no more than 150.0 mm, Margins or tooling bars should be added on the longest sides during production to prevent panel deformation.

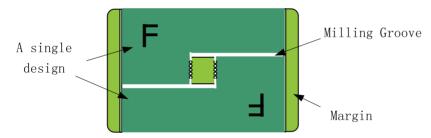

#### [10] Single Board Panelization

Regular shape board

Margins are not required for boards with v-cut grooves that satisfy the clearance area requirement stated in [4.1].

Figure 7: Example layout of step and repeat panelization

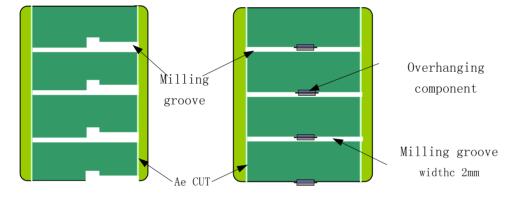

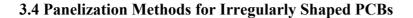

Irregularly shaped boards

A combination of v-cut lines and milling grooves can be used to shape irregularly shaped boards or boards where components hang over the edge.

Figure 8: Panelization of irregularly shaped PCBs

#### [11] Center Panelization

- Center panelization can be applied to irregularly shaped PCBs. They are arranged in such a way that the outer shape is regular.

- If the two boards do not fit together completely, milling can remove the excess and separate the boards.

- For larger pieces of excess material, the panel can be designed such that the excess pieces may be broken off using stamp hole connections. See figure 9.

**₯ FUSION**

#### One-Stop prototype in Seeed Fusion

Figure 9: Two irregular boards with the excess connected via stamp holes.

PCBs with gold finger connectors need to be positioned so that the fingers face outwards as shown in figure 10. This is necessary for the gold plating process.

Figure 10: Recommended layout of PCBs with gold fingers.

#### [12] Symmetrical Panelization

If the SMD of cell board both sides meet the requirement of back reflow soldering, you can use the mirror symmetry splice board.

Note: Mirror symmetry panelization requires that the design mirrors the original exactly, for example for a 4-layer board, if the second layer is the negative power / ground plane, then the third layer must also be negative. Otherwise mirror symmetry panelization cannot be used.

Figure 11: Mirror panelization

Fiducial marks on the mirrored boards must match after flipping. For specific placement requirements, please refer to the Fiducial mark design section later in this document.

#### [13] General principle

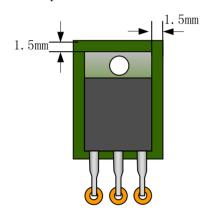

- If the assembled PCB does not have a clearance area of 5mm along the edge of the board, margins/tooling bars should be added along its perimeter.

- If the PCB is irregular in shape, for example, a corner is missing or a segment cuts into the board, block filler pieces should be used to make the outline more rectangular in shape to aid assembly.

Figure 12: Completing the PCB outline of irregularly shaped boards.

[14] It is recommended that SMT and wave soldering techniques be used for irregular boards with filler pieces larger than 35mm x 35mm. For filler pieces greater than 50mm in length, two sets of stamp holes should be used, otherwise, one set is satisfactory.

Figure 13: Stamp hole placement for filler pieces greater than 50mm in length.

#### 4. Component Layout Considerations

#### 4.1 General Component Layout Requirements

[15] Through-hole components with polarity or direction requirements should maintain a consistent alignment

throughout the layout and should be arranged as neat as possible. For SMD devices, if they cannot be placed in the same direction, they should be consistent in both X and Y directions for example for tantalum capacitors.

- [16] If the component needs to be glued, ensure the component has at least 3mm space.

- [17] For PCBs which need have heatsinks, the location and orientation of the heatsink should be considered. There must be sufficient space to ensure that the heatsink does not touch other components. Ensure that a minimum distance of 0.5mm is maintained.

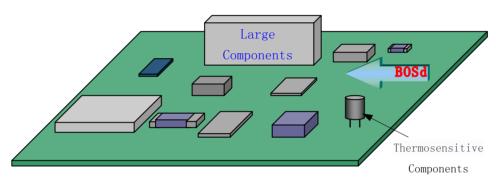

- Description: 1. Thermosensitive devices (such as resistive capacitors, crystal, etc.) should be situated far away from heat producing components.

- 2. Thermosensitive devices should be placed by an air outlet. Tall components devices should be placed behind shorter components to facilitate air flow.

Figure 14: Placement of thermosensitive components

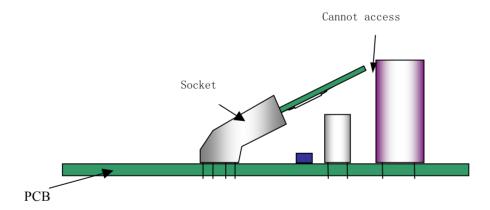

[18] The distance between the devices must satisfy the required space for normal operation, for example, a memory card socket.

Figure 15: Blocked socket.

[19] Metal parts with different properties or devices with metallic cases must not touch each other. A minimum distance of 1.0mm should be maintained between components.

#### 4.2.1 General Requirements for SMD Components

- [20] It is recommended that fine pitch devices be placed on the same side of the PCB and larger devices (such as inductors) be arranged on the top side.

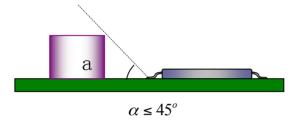

- [21] Polarized components should be aligned such that all the positive poles are on one side of the board and negative poles on the other where possible. Avoid positioning taller components next to shorter ones, which may hinder inspection. A viewing angle of no less than 45 degrees must be maintained throughout the layout to aid manual solder joint inspection.

Figure 16: Solder joint inspection angle.

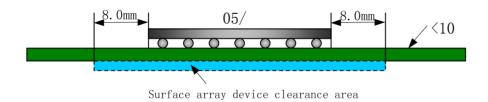

- [22] Surface array devices such as CSP, BGA, etc. must have a clearance area of 2mm, but 5mm is ideal.

- [23] In general, surface array devices should not be placed on the bottom side of the board. In the event there is, other surface array devices should not be placed on the top side, in a region including the outline of the surface array device extending 8.00mm outwards, see Figure 17; In the event there is, the same region on the top layer, with an additional 8mm boarder about this region, must not contain surface array devices.

Figure 17: Layout requirements for surface array devices

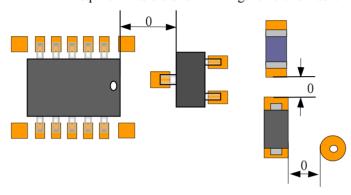

#### **4.2.2 SMD Component Placement Requirements**

- [24] All SMD components shall be smaller than 50mm on at least one side.

- [25] It is not recommended for two surface-mount gullwing pin devices to overlap, for example, SOP packages as shown in Figure 18.

Not recommended

Figure 18: Incompatible layout of two SOP footprints.

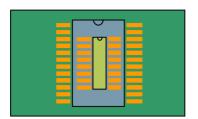

[26] In the event that solder pads are shared between two SMD components, the packages must be the same, see Figure 19.

Figure 19: Sharing of solder pads for SMD components.

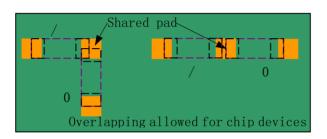

[27] Through-hole devices and SMD components are allowed to overlap when it can be confirmed that the SMD pad and the solder paste printed thereon has no effect on the soldering of the through-hole device. See Figure 20.

Through-hole components may overlap SMD components

Figure 20: Acceptable through-hole and SMD component layout design.

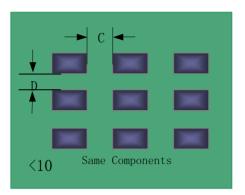

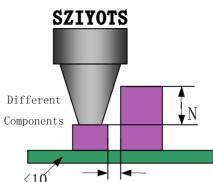

[28] The required distance between SMD components is

Same component:  $\geq 0.3$ mm

Different components:  $\geq 0.13 \times h + 0.3$ mm (where h is the maximum height difference of the surrounding neighbors)

Figure 21: Spacing requirements for components.

[29] For PCBs requiring solder reflow, SMT device spacing varies according to the table 1.

Description: The quoted value is the largest of the two: either the pad or the body of the device, whichever is most applicable. The values in brackets represent the lowest acceptable value.

Table 1: Components spacing requirements.

| (Units in mm) | 0402 ~ 0805 | 1206 ~ 1810 | STC3528 ~ 7343 | SOT / SOP | SOJ / PLCC | QFP  | BGA        |

|---------------|-------------|-------------|----------------|-----------|------------|------|------------|

| 0402 ~ 0805   | 0.40        | 0.55        | 0.70           | 0.65      | 0.70       | 0.45 | 5.00(3.00) |

| 1206 ~ 1810   |             | 0.45        | 0.65           | 0.50      | 0.60       | 0.45 | 5.00(3.00) |

| STC3528 ~     |             |             | 0.50           | 0.55      | 0.60       | 0.45 | 5.00(3.00) |

| SOT / SOP     |             |             |                | 0.45      | 0.50       | 0.45 | 5.00       |

| SOJ / PLCC    |             |             |                |           | 0.30       | 0.45 | 5.00       |

| QFP           |             |             |                |           |            | 0.30 | 5.00       |

| BGA           |             |             |                |           |            |      | 8.00       |

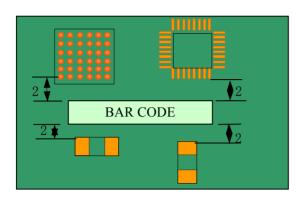

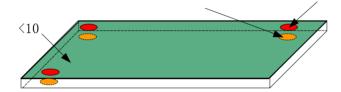

[30] The distance between fine pitch devices and the board edge must be greater than 10mm so as to not adversely affect printing quality.

Recommendation: Ideally, the distance between the bar code frame and the surface mounted components should meet the requirements shown in Table 2 to preserve the quality of the solder.

Table 2: Recommended spacing requirements between printed barcodes and component footprints

| Component<br>Type     | Pitch ≤ 1.27mm's Gullwing Pin (e.g. SOP, QFP) and Surface Array Components | 0603 Size and Greater SMD Chip Components and Other Footprints |

|-----------------------|----------------------------------------------------------------------------|----------------------------------------------------------------|

| Minimum<br>Spacing, D | 10mm                                                                       | 5mm                                                            |

Figure 22: Layout requirements of printed barcodes and components

#### 4.2.3 Through-Hole Component Layout Requirements for PCBs Undergoing Reflow Soldering

- [31] For PCB with non-transmission side larger than 300mm, heavier through-hole components should not be placed in the middle of the PCB. This will reduce the board deformation caused by the weight of the components during soldering.

- [32] To facilitate plug-in sockets, the socket should be placed where convenient.

- [33] The distance between through-hole components should be > 10mm.

- The distance between through-hole components and the transmission edge should be  $\geq 10$ mm, and non-transmission edge should be  $\geq 5$ mm.

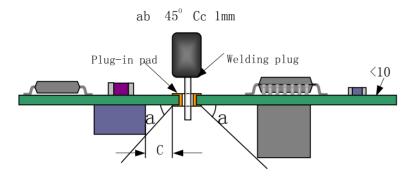

#### 4.3 Wave Soldering

#### 4.3.1 SMD Component Layout Requirements for PCBs Undergoing Wave Soldering

- [35] Wave soldering is suitable for the following SMD components:

- Chip resistors, capacitors, and inductors that have a package size greater or equal to 0603 and standoff value less than 0.15mm.

- SOP packages with pitch  $\geq 1.27$ mm and Standoff value  $\leq 0.15$ mm.

- SOT packages with pitch  $\geq 1.27$ mm and visible pins.

Note: The pins of SMD components undergoing wave soldering must be less or equal to 2mm. Other components must be less than 4mm in height.

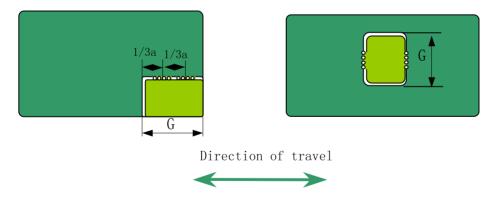

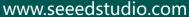

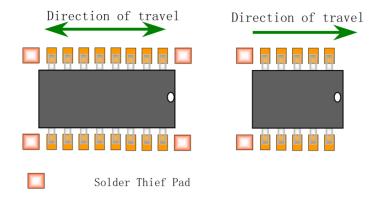

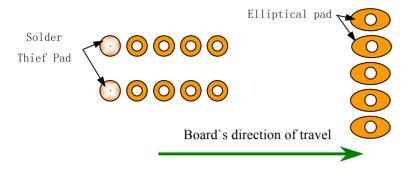

[36] The long axis of SOP package components should be perpendicular to the direction of travel of the solder wave in the wave soldering process. SOP components also need extra pads at the end of the solder pad rows to act as 'solder thieves,' see Figure 23.

Figure 23: Solder thief pad placement for SOP packages undergoing wave soldering.

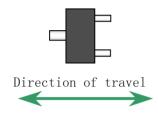

The orientation of SOT-23 package components should be such that the pins point parallel to the direction of travel.

Figure 24: Orientation of SOT-23 packages undergoing wave soldering.

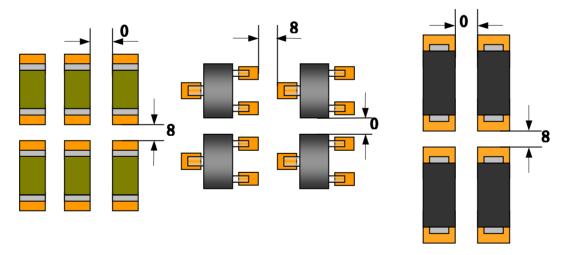

- [38] General component spacing principles: In order to reduce shadow effect problems caused by wave soldering, certain distances must be maintained between components and individual pads.

- For components of the same type according to Table 3:

Figure 25: Layout of components of the same type.

Table 3: Distances between components of the same type.

|           | Pad Spacing L (mm/mil) |             | Component Spacing B (mm/mil) |             |

|-----------|------------------------|-------------|------------------------------|-------------|

| Footprint | Minimum                | Recommended | Minimum Specing              | Recommended |

| Footprint | Spacing                | Spacing     | Minimum Spacing              | Spacing     |

| 0603      | 0.76/30                | 1.27/50     | type0.76/30                  | 1.27/50     |

| 0805      | 0.89/35                | 1.27/50     | 0.89/35                      | 1.27/50     |

| ≥ 1206    | 1.02/40                | 1.27/50     | 1.02/40                      | 1.27/50     |

| SOT                 | 1.02/40 | 1.27/50 | 1.02/40 | 1.27/50  |

|---------------------|---------|---------|---------|----------|

| Tantalum Capacitors | 1.02/40 | 1.27/50 | 1.02/40 | 1.27/50  |

| 3216 and 3528       | 1.02/40 | 1.27/30 | 1.02/40 | 1.27/30  |

| Tantalum Capacitors | 1.27/50 | 1.52/60 | 2.03/80 | 2.54/100 |

| 6032 and 7343       | 1.27/30 | 1.32/00 | 2.03/80 | 2.34/100 |

| SOP                 | 1.27/50 | 1.52/60 |         |          |

• For different component types, the solder pad edge spacing should be  $\geq 1.0$ mm. Distance requirements are shown in Figure 26 and Table 4.

Figure 26: Layout of components of different types and PCB structures.

Form 4: Distances between components of different types and PCB structures.

| Footprint (mm/mil)          | 0603 -<br>1810 | SOT      | SOP      | Through-<br>Holes | Vias   | ICT Point | Solder<br>Thief Pad<br>Edge |

|-----------------------------|----------------|----------|----------|-------------------|--------|-----------|-----------------------------|

| 0603 -<br>1810              | 1.27/50        | 1.52/60  | 2.54/100 | 1.27/50           | 0.6/24 | 0.6/24    | 2.54/100                    |

| SOT                         | 1.27/50        |          | 2.54/100 | 1.27/50           | 0.6/24 | 0.6/24    | 2.54/100                    |

| SOP                         | 2.54/100       | 2.54/100 |          | 1.27/50           | 0.6/24 | 0.6/24    | 2.54/100                    |

| Through-<br>Holes           | 1.27/50        | 1.27/50  | 1.27/50  |                   | 0.6/24 | 0.6/24    | 2.54/100                    |

| Vias                        | 0.6/24         | 0.6/24   | 0.6/24   | 0.6/24            | 0.3/12 | 0.3/12    | 0.6/24                      |

| ICT Point                   | 0.6/24         | 0.6/24   | 0.6/24   | 0.6/24            | 0.3/12 | 0.6/24    | 0.6/24                      |

| Solder<br>Thief Pad<br>Edge | 2.54/100       | 2.54/100 | 2.54/100 | 2.54/100          | 0.6/24 | 0.6/24    | 0.6/24                      |

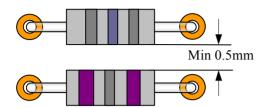

#### 4.3.2 Common Through-Hole Component Layout Requirements

[39] In addition to the special requirements relating to the specific structure of the device, through-hole

components must be placed on the top layer.

[40] The spacing between adjacent components is shown in Figure 27.

Figure 27: Distance between through-hole components.

[41] In order to facilitate manual soldering and maintenance/repair the conditions shown in Figure 28 must be satisfied.

Figure 28: Through-hole placement requirements.

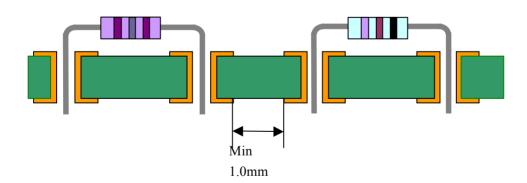

#### 4.3.3 General Requirements For Wave Soldering Through Hole Components

The optimum component pitch is  $\geq 2.0$ mm, the distance between the solder pad edges must be at least 1.00mm as shown in Figure 29. In addition, the component bodies must not interfere with each other.

Figure 29: Through-hole component layout for wave soldering.

[43] For a long row of through hole component holes, the components should be positioned such that the row is parallel to the direction of travel of the solder wave. In special circumstances where the row of pads must be aligned perpendicular to the direction of travel, suitable adjustments should be made, such replacing the standard pads with elliptical pads. When the spacing between adjacent pad edges is 0.6mm-1.0mm, the

implementation of oval pads or solder thieves is recommended.

Figure 30: Solder pad alignment relative to board's direction of travel through the wave soldering equipment

#### 5. Hole Design

#### 5.1 Vias

#### 5.1.1 Hole Spacing

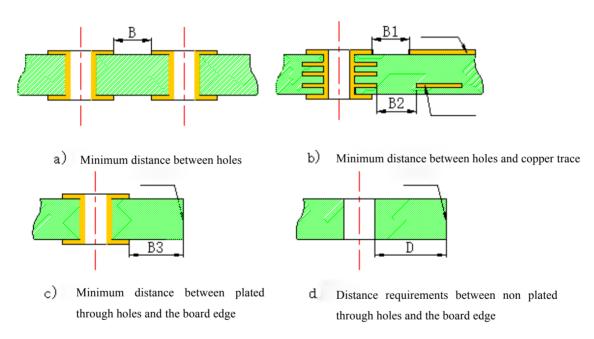

Figure 31: Spacing requirements for holes and vias

- [44] The spacing between holes must satisfy  $B \ge 5$ mil.

- [45] The spacing between holes and any copper trace/pour must satisfy: B1 & B2  $\geq$  5mil.

- [46] The spacing between plated through holes (PTH) to the board edge: B3≥20mil.

- [47] The recommended minimum distance from non-plated through holes (NPTH) wall to the board edge is D ≥ 40mil.

#### 5.1.2 Via Clearance Area

- [48] Via holes must not overlap solder pads.

- [49] Via holes must not be in a region that extends 1.5mm from the metal shell of any components.

#### 5.2 Mechanical Hole Design

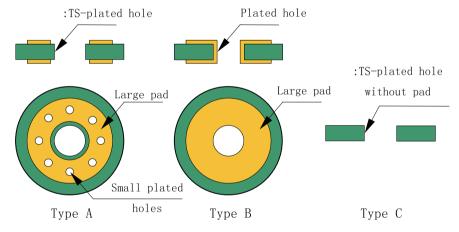

#### 5.2.1 Hole Types

Table 5: Recommended hole designs according to function

| Soldering Process  | Metal Fastener | Non-Metallic<br>Fastener | Metal Plated<br>Rivet | Non-Metallic<br>Rivet | Board Positioning (Fiducials) |

|--------------------|----------------|--------------------------|-----------------------|-----------------------|-------------------------------|

| Wave soldering     | Type A         |                          |                       |                       |                               |

| Non Wave soldering | Туре В         | Type C                   | Type B                | Type C                |                               |

Figure 32: Structure of mechanical holes.

#### **5.2.2 Spacing Requirements**

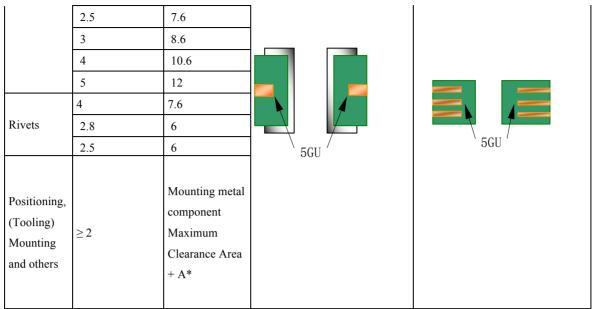

Table 6: Spacing requirements for mechanical holes according to type.

|        |                        |                                            | Minimum Copper Clearance Area (mm)                    |                                                                                    |  |  |  |

|--------|------------------------|--------------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------|--|--|--|

| Туре   | Fastener Diameter (mm) | Surface<br>Clearance Area<br>Diameter (mm) | Minimum distance between plated hole and inner trace. | Minimum distance between plated holes and the trace of the ground and power planes |  |  |  |

| Screws | 2                      | 7.1                                        | 0.4                                                   | 0.63                                                                               |  |  |  |

(FUSION

#### One-Stop prototype in Seeed Fusion

<sup>\*</sup> Where 'A' is the minimum spacing between the hole and the trace, with no minimum copper area in the inner layer.

#### 6. Solder Mask Design

#### 6.1 Solder Mask Design for Copper Traces

[50] Generally, solder mask will cover copper traces, but in special cases, traces can be exposed according to the specific requirements.

#### 6.2 Solder Mask Design for Holes

#### 6.2.1 Via Holes

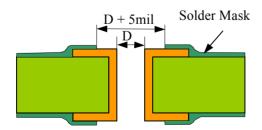

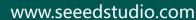

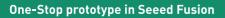

[51] Via holes should have solder mask openings on both sides of the board centered about the hole, as shown in Figure 33. The required diameter of the opening should be D + 5mil where D is the diameter of the plated hole.

Figure 33: Solder Mask opening for via holes.

[52] For metallic rivet holes, the solder mask opening should be centered about the rivet hole with a diameter + 6mil of the plated pad, on both sides.

Figure 34: Metallic rivet hole solder mask opening.

[53] For non-plated rivet holes, the solder mask opening should be greater than the clearance area for the screw head.

D c Clearance area of the installation screw head

Figure 35: Non-metallic rivet hole solder mask opening.

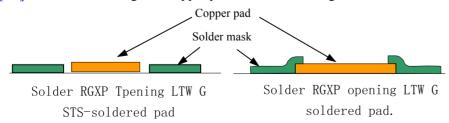

[54] The solder mask openings for Type A wave soldered holes should satisfy:

Type / hole bottom side solder mask opening.

0 0 d 0 d+5mil

Type / hole YTU side solder RGXP opening

$\boldsymbol{D}$  c Clearance area of the screw head

Figure 36: Type A mechanical hole solder mask opening.

#### **6.2.3 Positioning Holes**

[55] The solder mask opening on the front and back sides of non-plated holes should be D+10mil, concentric about the hole, where D is the diameter of the non-plated hole.

Figure 37: Solder mask opening for non-plated mechanical holes.

#### 6.2.4 Buried and Plugged Vias

- [56] Internal vias (buried vias) do not require solder mask openings on either side of the board.

- [57] For PCBs requiring wave soldering or if the board has BGA (or CSP) with a pitch smaller than 1.00mm, the BGA via hole should be plugged.

- [58] If an in circuit testing (ICT) point is added under the BGA, it is recommended to lead out the testing pad from the via hole as shown in figure 38. The diameter of the test pads should be 32mil; solder mask opening is 40mil.

Figure 38: BGA Testing pad.

[59] If the PCB does not require wave soldering, and the pitch of BGA components is greater that 1.00mm, then there is no need for plugged vias. The BGA via itself can be used as a test point. The top side solder mask opening should be 5mil bigger than the diameter of the hole. The bottom side testing pad should be 32mil with a solder mask opening of 40mil.

#### 6.3 Solder Pad Solder Mask Design

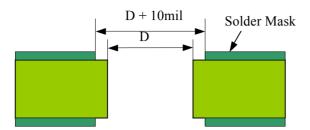

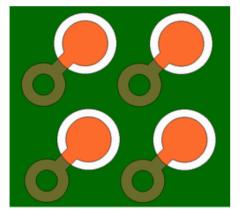

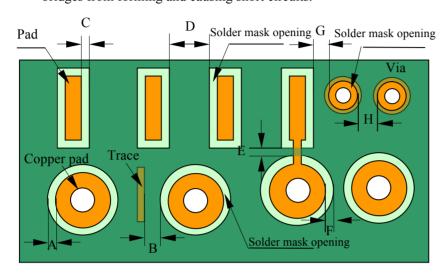

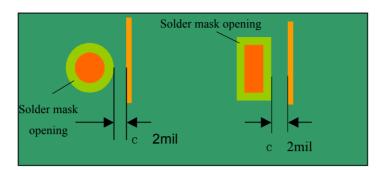

[60] Solder mask design for copper pads should follow figure 39.

Figure 39: Solder mask openings for copper pads

[61] Since PCB manufacturers have limited precision and limits on the minimum width of solder mask openings, solder mask openings should be at least 6mil bigger than pad size (3mil each side), with a minimum solder mask bridge width of 3mil. There must be solder mask separating pads and holes to prevent solder bridges from forming and causing short circuits.

Figure 40: Solder mask openings and material widths for various copper pads.

Table 7: Recommended minimum solder mask material width between pads.

| Туре                           | Minimum (mil) |

|--------------------------------|---------------|

| Solder mask opening (A)        | 3             |

| Solder mask material width (B) | 2             |

| Solder mask opening (C)        | 3             |

| Solder mask material width (D) | 3             |

| Solder mask material width (E) | 3             |

| Solder mask material width (F) | 3             |

| Solder mask material width (G) | 3             |

| Solder mask material width (H) | 3             |

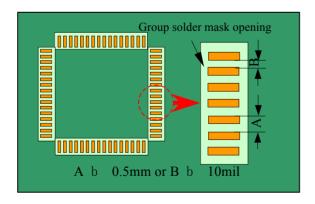

[62] Groups of SMD pads less than 0.5mm (20mil) apart or less than 10mil between the pad edges do not need solder mask to separate them and can be opened as a group. See figure 41.

Figure 41: Solder mask openings for fine pitch SMD components.

[63] Solder mask openings are recommended for heatsink contacts.

#### 6.4 Gold-Finger Solder Mask Design

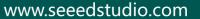

[64] The copper pads of gold-finger connectors should open up the solder mask together. The top of the pads (where the trace is connected) should be opened flush with the solder mask material, and the bottom end solder mask opening should close beyond the edge of the board, as shown in figure 42.

Figure 42: Solder mask opening for a gold-finger

#### 7. Copper Trace Design

#### 7.1 Trace Width, Spacing and Routing Requirements

[65] The width and spacing of copper traces vary according to the thickness of the copper material and which layer the trace is located. Recommended trace widths and spacing for inner and outer layers of various copper thicknesses is shown in table 8.

Table 8: Recommended trace widths and spacing.

| Copper Thickness (oz) | Outer Layer Trace Width/Spacing (mil) | Inner Layer Trace Width/Spacing (mil) |

|-----------------------|---------------------------------------|---------------------------------------|

| H, 1                  | 4/5                                   | 4/4                                   |

| 2                     | 6/6                                   | 6/6                                   |

| 3                     | 8/8                                   | 8/8                                   |

[66] For outer layers, the distance between the trace and copper pads should satisfy the requirements shown in figure 43.

Figure 43: Recommended spacing between trace and pads.

- [67] The distance between outer layer traces, inner layer power/ground planes and ground bus traces to the board edge should be greater than 20mil.

- [68] There should not be any traces going through the metal shell of components (e.g. heatsink). The region of components' metal shell should have a 1.5mm clearance area around it.

Figure 44: Clearance area of components with metal cases.

[69] Distance from the trace to non-plated through holes is summarised in table 9.

Table 9: Distance from the trace to the edge of NPTHs.

| Aperture Size           | Distance From the Trace to the Hole Edg | ge                            |

|-------------------------|-----------------------------------------|-------------------------------|

| NPTH < 80mil            | Mounting hole                           | Refer to Mounting hole design |

| NP1H < 80IIII           | Non Mounting hole                       | 8mil                          |

| 80mil < NPTH < 120mil   | Mounting hole                           | Refer to Mounting hole design |

| 80IIII < NP1H < 120IIII | Non Mounting hole                       | 12mil                         |

| NPTH > 120mil           | Mounting hole                           | Refer to Mounting hole design |

| INF 1 F1 > 120HHI       | Non Mounting hole                       | 16mil                         |

#### 7.2 Solder Pad to Trace Connections

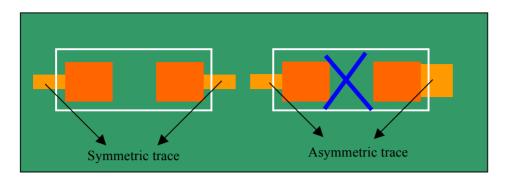

[70] Asymmetry should be avoided in the trace and connected solder pads.

Figure 45: Symmetric and asymmetric traces

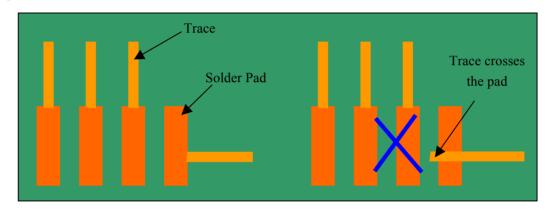

[71] Traces should start from the center of solder pads

Figure 46: Starting position of the trace to the pad.

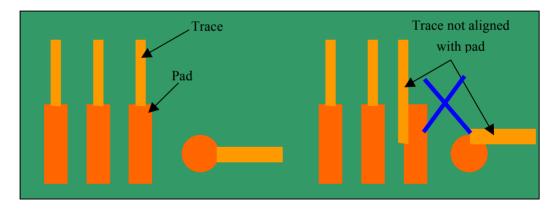

Figure 47: Trace and pad alignment.

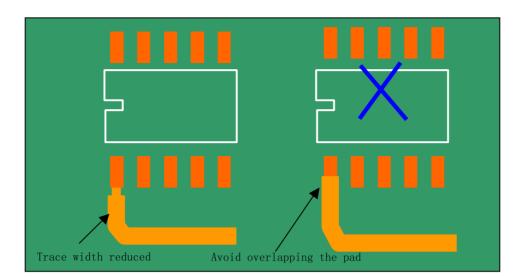

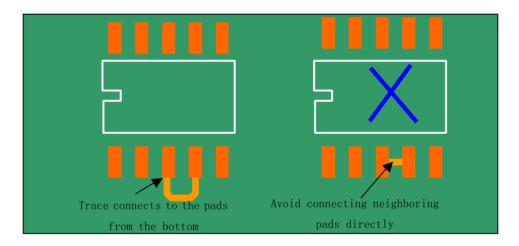

[72] When the width of the trace is wider than the pad, the trace should not overlap the pad. The trace width should be reduced at the point of contact as shown in figure 48. When adjacent pins of fine pitch components need to be connected, the trace should not run directly between the pads. Instead, it should run outside of the row and connect as shown in figure 49.

FUSION

One-Stop prototype in Seeed Fusion

Figure 48: Connecting the trace and pad when the trace width is larger.

Figure 49: Connecting adjacent pads of fine pitch components

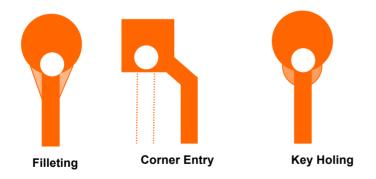

[73] The below designs are recommended for ensuring a strong connection between a trace and hole.

Figure 50: Connections between the trace and holes

#### 7.3 Copper Pour Design Requirements

- [74] When the traces on the same layer are unevenly distributed, or the copper distribution in different layers is asymmetric, including a hatched style copper pour grid into the design is recommended

- [75] If there is a large section of the board without copper, copper pour can be used to even out the copper distribution.

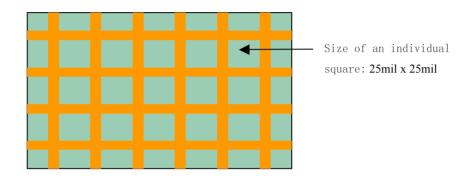

- [76] Recommended copper grid size is about 25mil x 25mil.

Figure 51: Copper grid design.

#### 8. Silkscreen Design

#### 8.1 Silkscreen Design Considerations

#### [77] General Requirements

- The width of the silkscreen line should be greater than 5mil. Designers must ensure that the silkscreen character's height is large enough to be read by the naked eye (recommended h 50mil).

- Recommended spacing between silkscreen objects is h 8mil.

- The silkscreen must not overlap with solder pads or Fiducials. The minimum spacing between both is 6mil.

- White should be the default silkscreen ink color. Special requirements should be specified in the PCB's drill hole layer

- For high-density PCB design, the contents of the silkscreen can be chosen according to specific requirements. Any silkscreen text should follow the convention of left to right, top to bottom.

#### 8.2 Silkscreen Contents

- [78] The contents of the silkscreen can include PCB name, version, component serial number, polarity and direction label, barcode box, mounting hole location code, component footprint, board direction of travel indicator, anti-static label, heatsink label, etc.

- [79] PCB board name and version:

Board name and version should be placed on the top side of the PCB. The font should be chosen such that it

can be easily read. The top and bottom sides of the PCB should also be marked with 'T' and 'B' (or similar).

#### [80] Barcode (optional):

- The barcode should be orientated horizontally or vertically on the PCB, refrain from orientating the barcode at any other angle.

- The recommended position of the bar code on a typical board is shown in the figure below; the position on non-standard boards can use this for reference.

Figure 52: Barcode recommended positioning.

#### [81] Component silk screen:

- Component labels, mounting holes and positioning holes must be indicated on the silkscreen clearly and should be located by the relevant features.

- Silkscreen characters, polarity and direction labels must not be covered by components.

- For components installed horizontally (such as lying electrolytic capacitors), the silkscreen should include the component outline on the corresponding position.

#### [82] Mounting holes, pilot hole:

It is recommended that the locations of the mounting holes and pilot holes on the PCB be labelled as "M \*\*" and "P \*\*," respectively.

#### [83] Direction of travel:

For the PCBs that are required to be fed into equipment, such as wave soldering equipment, in a specific orientation, the direction of travel should be indicated on the board. This is also suitable for PCBs with solder thieves and teardrop solder pads.

#### [84] Heatsink:

For power PCBs that require a heatsink, if the projected area of the heatsink is larger than the component, the actual size must be indicated on the silkscreen.

#### [85] Anti-Static Label:

The anti-static silk screen should preferentially be placed on the top side of the PCB.

FUSION

#### 9. PCB Lamination Structure

#### 9.1 Layer Structure

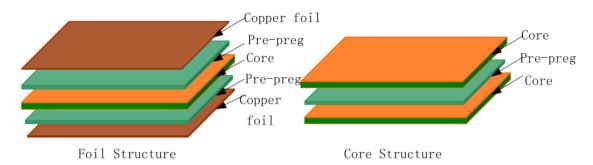

[86] The foil stacking structure is recommended.

Description: For PCB lamination, there are generally two design types: Copper foil structure and Core board structure. The Core board type is used in special multilayered boards and mixed boards.

Figure 53: PCB lamination types.

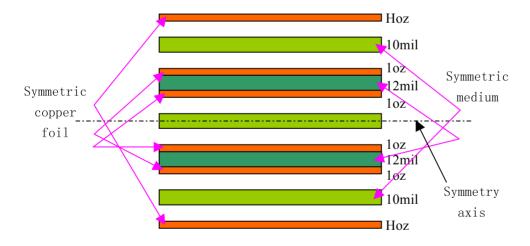

- [87] 0.5oz copper foil is generally used for the copper in the outer layers, whereas 1oz copper foil is generally chosen for the inner layers. Core boards with asymmetric thicknesses should be avoided in the inner layers.

- [88] Symmetrical design considerations include the thickness of pre-preg layers, the type of resin used, the thickness of the copper foil and the type of layer distribution (copper foil layer, circuit layer). The layout should be as symmetrical as possible about the symmetry axis.

Figure 54: Symmetrical design diagram

#### 9.2 Layer Thickness Requirements

[89] Standard PCB layer thicknesses are summarized in table 10.

Table 10: Standard layer thicknesses

FUSION

| Board Type (4-layer) | 1-2  | 2-3  | 3-4  | 4-5 | 5-6 | 6-7 | 7-8 | 8-9 | 9-10 | 10-11 | 11-1 |

|----------------------|------|------|------|-----|-----|-----|-----|-----|------|-------|------|

| 1.6mm                | 0.36 | 0.71 | 0.36 |     |     |     |     |     |      |       |      |

| 2.0mm                | 0.36 | 1.13 | 0.36 |     |     |     |     |     |      |       |      |

| 2.5mm                | 0.40 | 1.53 | 0.40 |     |     |     |     |     |      |       |      |

| 3.0mm                | 0.40 | 1.93 | 0.40 |     |     |     |     |     |      |       |      |

# 10. PCB Dimensions Specification

#### 10.1 Manufactured PCB Dimensions

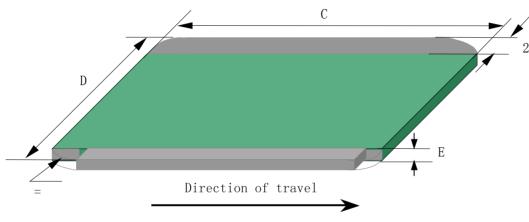

[90] The range of dimensions allowed for each type of PCB construction is shown in table 11.

Figure 55: PCB dimensions description.

Table 11: PCB dimensions and weight requirements.

| РСВ Туре                       | Length, X (mm)  | Width, Y (mm) | Thickness, Z (mm) | Assembled Weight (Reflow Soldering) | Bevel (mm)   | Assembled<br>Weight (Wave<br>Soldering) | Primary Side Components/ Solder Joint Clearance Area, D (mm) |

|--------------------------------|-----------------|---------------|-------------------|-------------------------------------|--------------|-----------------------------------------|--------------------------------------------------------------|

| Single Sided<br>Mounting       | 51.0 ~<br>508.0 | 51.0 ~ 457.0  | 1.0 ~ 4.5         | ≤ 2.72kg                            | ≥ 3d 120mil) |                                         | 5.0                                                          |

| Single Sided Mixed Mounting    | 51.0 ~<br>490.0 | 51.0 ~ 457.0  | 1.0 ~ 4.5         | ≤ 2.72kg                            | ≥ 3d 120mil) | ≤ 5.0kg                                 | 5.0                                                          |

| Double Sided<br>Mounting       | 51.0 ~<br>508.0 | 51.0 ~ 457.0  | 1.0 ~ 4.5         | ≤ 2.72kg                            | ≥ 3d 120mil) |                                         | 5.0                                                          |

| Double Sided<br>Mixed Mounting | 51.0 ~<br>490.0 | 51.0 ~ 457.0  | 1.0 ~ 4.5         | ≤ 2.72kg                            | ≥ 3d 120mil) | ≤ 5.0kg                                 | 5.0                                                          |

- [91] Required PCB width-to-thickness ratio =  $Y / Z \le 150$ .

- [92] Required PCB length-to-width ratio =  $X / Y \le 2$ .

- [93] For board thicknesses of less than 0.8mm, the copper foil of should be evenly distributed to prevent board

bending. If there are many small boards, use of a fixture is recommended.

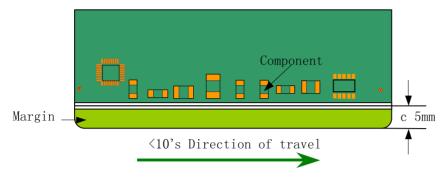

[94] If the primary side does not meet the clearance area requirements, then the addition of a margin of a width greater than 5mm, along the direction of travel is recommended.

Figure 56: PCB minimum margin dimensions.

- [95] The body of components must not exceed past the edge of the PCB, and must satisfy the following:

- The minimum distance from the edge of the solder pad (or component body) to the primary side must be less than 5mm.

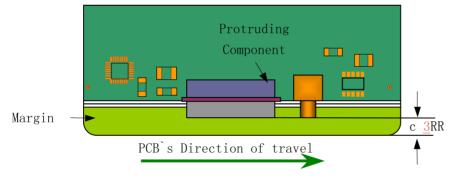

- For non-reflow soldering, when a component protrudes out from the PCB, the width of the margin is as follows:

Figure 57: Protruding component margin requirements.

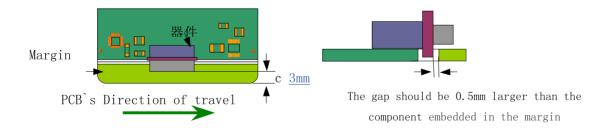

For non-reflow soldering, when a component protrudes out from the PCB, the component must fit into the margin with 0.5mm clearance as shown in Figure 58.

Figure 58: Protruding component margin gap requirements.

#### 11. Fiducial Mark Design

#### 11.1 Classification

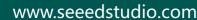

[96] Fiducial marks are divided into three categories according to their position and role: Panel Fiducials, Image Fiducials and Local Fiducials.

Figure 59: Classification of Fiducial Marks.

#### 11.2 Fiducial Mark Structure

#### 11.2.1 Panel Fiducial Marks and Image Fiducial Marks

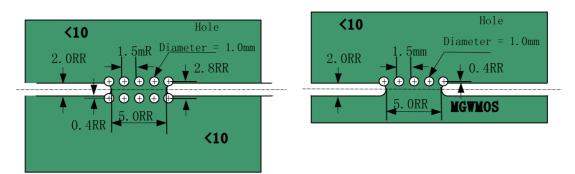

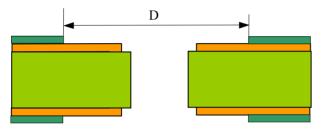

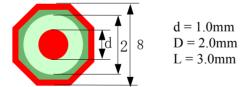

[97] Size/Shape: a solid filled circle with a diameter of 1.0 mm.

Solder mask opening: 2.00mm in diameter and concentric with the Fiducial.

Covering copper: an octagonal copper ring 3.00mm in diameter concentric with the Fiducial and clearance Area.

Figure 60: Structure of Panel and Image Fiducials.

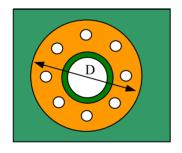

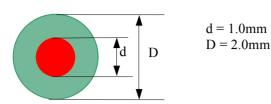

#### 11.2.2 Local Fiducial

[98] Size/Shape: a solid filled circle with a diameter of 1.0mm.

Solder mask opening: 2.00mm in diameter and concentric with the Fiducial.

Covering Copper: not needed.

Figure 61: Structure of local Fiducials.

#### 11.3 Position of Fiducials

[99] In General: PCBs which require SMT automated assembly must have Fiducial marks on the necessary layers. PCBs which only require manual soldering do not require Fiducial marks.

For single-sided boards, Fiducial marks are only required on the side where the SMD components are to be

For double-sided boards, both sides must have Fiducial marks. The position of the Fiducial marks must be generally consistent (except for mirror panels).\*\*

> Top side Fiducial Bottom side Fiducial

Figure 62: Both sides of a double sided PCB should generally be consistent with each other.

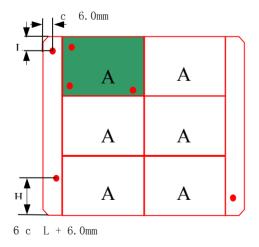

#### 11.3.1 Panel Fiducial Marks

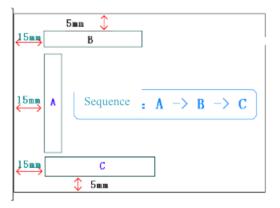

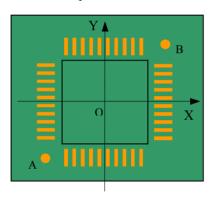

[100] Panel Fiducials and image Fiducials should be located on the panel margins and on individual sub-boards respectively. There should be three panel Fiducials per board and three local Fiducials per sub-board, arranged in an 'L' shape as far from each other as possible, as shown in Fig. 63:

Figure 63: Fiducial positioning requirements on the panel margins and individual boards. When using mirrored panelization, the panel Fiducial marks must be consistent after flipping.

#### 11.3.2 Image Fiducial Marks

[101] There must be three Fiducial marks per sub-board, arranged in an 'L' shape, located as far as possible from each other. The distance from the origin of the Fiducial mark and the edge of the sub-board should be greater than 6.00mm. If it is not possible to ensure that the four edges satisfy this requirement, then the requirement must be satisfied for the primary side at least.

#### 12.3.3 Local Fiducial Marks

[102] For devices with gullwing pins and a pin pitch of  $\leq 0.4$ mm, and surface array packaged devices with a pin pitch of  $\leq 0.8$ mm, local Fiducial points are required.

Two local Fiducial marks are required per component and must be symmetrical on both sides of the origin of the component.

Figure 64: Local Fiducials must be symmetrical about the component's origin.

#### 12. Surface Treatment

#### 12.1 Hot Air Solder Leveling (HASL)

#### 12.1.1 Process Requirements

The PCB is covered with molten tin-silver alloy and the excess is blown off using hot air. The resulting alloy coating on the exposed copper surfaces must be between 1 µm to 25 µm.

#### 12.1.2 Range of Applications

[104] Using HASL, it is difficult to control the thickness of the coating and preserve the precise shape of the copper pads. It is not recommended for PCBs with fine pitch components since the copper pads of fine pitch components typically need to be flatter. In addition, the thermal shock of the HASL process may cause the PCB to warp. Therefore ultra-thin PCBs with a thickness of less than 0.7 mm are not recommended to undergo this type of surface treatment.

#### 12.2.1 Process Requirements

[105] Electroless Nickel Immersion Gold (ENIG) is a surface treatment involving plating the copper pads with nickel then immersion gold to help prevent it from oxidation. PCB copper metal surfaces treated with ENIG must have a nickel coating thickness of 2.5 µm-5.0 µm, and the immersion gold (99.9% pure gold) layer thickness must be 0.08µm-0.23µm.

#### 12.2.2 Range of Applications

[106] Due to the resulting flat surface, this process is suitable for PCBs with fine pitch components.

#### 12.2.3 Organic Solderability Preservatives (OSP)

[107] This process covers the exposed copper pads with a thin coat of an organic compound. Currently, the only recommended organic formula is Enthone's Entek Plus Cu-106A, which results in a thickness of 0.2µm-0.5µm. Because of the incredibly flat coating, it is especially popular with PCBs with fine pitch components.

#### 13. Files for Manufacture Requirements

#### 13.1 Naming Requirements for Assembly Files

[108] Requires board name, version, panelization description and version information.

#### 13.2 Naming Requirements for Stencil Layout Files

[109] Requires board name and version description.

#### 13.3 Naming and Content Requirements for Drill Files

[110] Requires board name, version, base material, surface treatment method, board thickness, the number of layers, the arrangement of layers, diameters of drill holes, drill hole properties, dimensions with tolerances and any other special requirements.

# 14. Appendix

#### **14.1 PCBA Constructions**

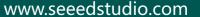

Single Sided (SMT) Mounting

Figure 65: Single Sided Mounting Illustration

Single Sided Mixed (SMT and THT) Mounting

Figure 66: Single Sided Mixed Mounting Illustration

Double Sided (SMT) Mounting

Figure 67: Double Sided Mounting Illustration

Wave-Soldered Double Sided Mixed (SMT and THT) Mounting

Figure 68: Wave-Soldered Double Sided Mixed Illustration

# Seeed Fusion Service One-stop prototyping service

Layout Service

Online instant quote

Experienced Engineers

#### **PCB** service

Layers1-16

Free Color Options6

Thickness0.6-3.0mm

Copper Weight1-3oz

Special Deals:\$4.9 for 10 pieces

#### **PCBA** service

One-stop PCBA without sourcing component Online instant quote

# 3D printing/CNC/Laser Cutting

Online instant quote

More than 10 material available

# **Open Parts Library**

In house stock for assembly

Eagle, Kicad, Altium library available

More than 600 components

# Why Choose us?

- Online instant quote without hidden cost

- Quick turn service with 24 hours build time

- Over 9 years experience with trusted capability

- Professional and thoughtful technical support

- Free online DFM Review (Design for Manufacturing)

- One-Stop Service, from electronic to mechanical

- ✓ 100% quality guarantee, offer free re-do if needed